Исследование

арифметического сумматора (Лабораторная работа)

Цель работы: исследовать

арифметический сумматор, полусумматор и полный сумматор.

Теория

Арифметические сумматоры – составная часть

арифметико-логических устройств (АЛУ) микропроцессоров (МП). Арифметический

сумматор состоит из двух устройств: полусумматора и n полных сумматоров.

Полный сумматор имеет три входа: A, B – входы суммируемых операндов, Ci –

вход переноса из предыдущего разряда сумматора и два выхода: S – выход полного сумматора и C0 – выход

переноса. Полусумматор отличается от полного тем, что у него нет входа переноса

из предыдущего разряда. Полусумматор используется в качестве первого разряда

арифметического сумматора, а в качестве остальных разрядов – полные сумматоры.

Полусумматор – одна из простейших комбинационных логических схем.

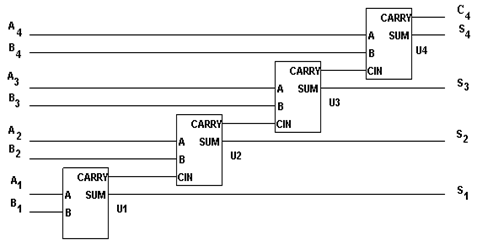

Рис. Четырехразрядный арифметический

сумматор

Рассматривая

таблицу истинности полусумматора можно заметить, что выход S полусумматора выполняет функции элемента «ИСКЛЮЧАЮЩЕЕ

ИЛИ», а выход переноса С полусумматора – элемента «И». Таким образом,

логические выражения для функций S и C равны:

S=AB′+A′B,

C=AB.

Таблица

Входы

|

Выходы

|

||

А

|

В |

S |

C |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

Схема полусумматора

представлена на рисунке далее.

Рис. Структура полусумматора

Из таблицы

истинности полного сумматора можно получить логические выражения для S (суммы) и C (переноса в следующий разряд). Логическое

выражение для S будет

иметь четыре слагаемых, соответствующих строкам таблицы, в которых выход S равен единице (стоки 4, 5, 7, 10),

S= A′B′Ci-1+A′BCi-1′+AB′Ci-1′+ABCi-1.

Таблица. Входы и

выходы

Входы

|

Выходы

|

|||

А

|

В |

Ci-1 |

S |

Ci |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

Логическое

выражение для C также

будет иметь четыре слагаемых (строки 6, 8, 9, 10):

Ci=A′BCi-1+A′BCi-1′+ABCi-1′+ABCi-1.

С помощью законов

булевой алгебры это выражение можно упростить, тогда оно будет иметь вид:

Сi=ACi-1+BCi-1+AB.

Схема полного сумматора

изображена далее.

Рис. Структура полного сумматора

Последовательность выполнение работы

1. Собрать (нарисовать) схему четырехразрядного

арифметического сумматора. Поместить на схему три 16-ричных индикатора и

генератор слова.

2. Открыть генератор слова и задать суммируемые

числа. Четыре младших разряда каждого генерируемого слова составляют первое

слагаемое (операнд). Следующие четыре разряда составляют второе слагаемое

(операнд).

3. Запустить процесс моделирования и следить за

показаниями индикаторов. Записать суммируемые числа и результат суммирования.

Рис. Схема исследования четырехразрядного

сумматора

4. Собрать схему и с

помощью логического анализатора, последовательно нажимая кнопки Circuit to Truth

Table (таблица истинности цепи) ![]() ,

Truth Table to Boolean Expression (булево выражение по

таблице истинности)

,

Truth Table to Boolean Expression (булево выражение по

таблице истинности) ![]() ,

Boolean Expression to Circuit (создание схемы по булеву выражению)

,

Boolean Expression to Circuit (создание схемы по булеву выражению) ![]() ,

получить:

,

получить:

· таблицу истинности полусумматора,

· логические выражения для выходов S и C,

· схемную реализацию логических выражений для

выходов S и C.

Рис. Схема исследования полусумматора:

a – выход S, б – выход C

5. Собрать схему и с помощью логического

анализатора получить таблицу истинности полного сумматора, логические выражения

для выходов S и C и схемную реализацию логических выражений.

Рис. Схема исследования полного сумматора:

a – выход S; б – выход C

Описание используемых контрольно-измерительных приборов

Генератор слова (Word Generator)

Генератор слова (или кодовый генератор) предназначен для генерации

32-разрядных двоичных слов, которые набираются пользователем в 16-ричном коде в

строке Hex или в двоичном коде в строке Binary на панели Edit .

Рис. Лицевая панель генератора слова

На панели Address расположены четыре

окна. Каждое кодовое слово из списка имеет адрес, выраженный 4-разрядным 16-ричным

числом.

В окне Edit отображается адрес

выбранного в таблице слова, в окне Current – адрес выдаваемого кодового слова.

В окне Initial устанавливается адрес

первого кодового слова множества слов, поступающих на выход генератора, в окне Final –

адрес последнего кодового слова множества слов, поступающих на выход генератора.

Для того

чтобы создать множество кодовых слов, выдаваемых генератором слова, нужно

ввести адрес первого и последнего слова в окно Initial и Final соответственно.

На панели Controls

устанавливается режим выдачи кодовых слов.

Чтобы выдать 32-разрядное слово на выход прибора, надо

щелкнуть по одной из кнопок Step,

Burst or Cycle. Номер этого

слова отобразится в окне Current

на панели Address.

Если необходимо выдать только одно слово, следует щелкнуть

по кнопке Step, если

все кодовые слова множества, то щелкнуть по кнопке Burst.

Если щелкнуть по кнопке Cycle, то будут выдаваться все кодовые слова множества непрерывно

циклически. Остановить выдачу слов можно, повторно щелкнув по кнопке Cycle.

Если нужно остановить и возобновить выдачу слов с определенного

слова, нужно щелкнуть по кнопке Breakpoint.

Чтобы установить контрольную точку (Breakpoint), нужно выбрать в списке

кодовое слово, на котором следует остановить вывод слов, и затем щелкнуть по

кнопке Breakpoint. У

этого слова появится метка в виде звездочки.

Чтобы удалить контрольную точку, нужно выбрать существующую

контрольную точку, затем щелкнуть по кнопке Breakpoint.

Можно установить

несколько контрольных точек. Контрольные точки могут использоваться как при

непрерывной (Cycle), так и при однократной (Burst) выдаче множества слов.

С помощью кнопки Pattern можно создавать новые или использовать ранее записанные

множества кодовых слов.

На панели Triggering расположены четыре

кнопки, с помощью которых можно установить источник запускающего сигнала

(внутренний (Internal)

или внешний (External))

и фазу запускающего сигнала (по переднему или заднему фронту).

На панели Frequency устанавливается

тактовая частота генератора слова в герцах, кило- или мегагерцах. Кодовые слова

поступают на выход генератора с каждым тактом генератора. Рядом расположена

клемма, на которую выдается сигнал готовности выдавать данные.

Логический преобразователь (Logic

Converter)

![]()

На лицевой панели преобразователя расположены

клеммы-индикаторы входов A,

B, C, …, H и клемма выхода Out,

окно для отображения таблицы истинности исследуемой схемы, строка для

отображения ее булева выражения и панель Conversions.

На панели Conversions

расположены шесть кнопок, используемых для получения:

·

![]() – таблицы истинности исследуемого устройства,

– таблицы истинности исследуемого устройства,

·

![]() – булева выражения, реализуемого исследуемым

устройством,

– булева выражения, реализуемого исследуемым

устройством,

·

![]() – минимизированного булева выражения;

– минимизированного булева выражения;

·

![]() – таблицы истинности по булевому выражению;

– таблицы истинности по булевому выражению;

·

![]() – схемы устройства по логическому выражению на

логических элементах без ограничения их типа,

– схемы устройства по логическому выражению на

логических элементах без ограничения их типа,

·

![]() –

создания схемы устройства только на логических элементах «И-НЕ».

–

создания схемы устройства только на логических элементах «И-НЕ».

Рис. Лицевая панель логического

преобразователя

Содержание

отчета

Отчет должен включать:

1) название пункта работы,

2) исследуемую схему,

3) результат моделирования.